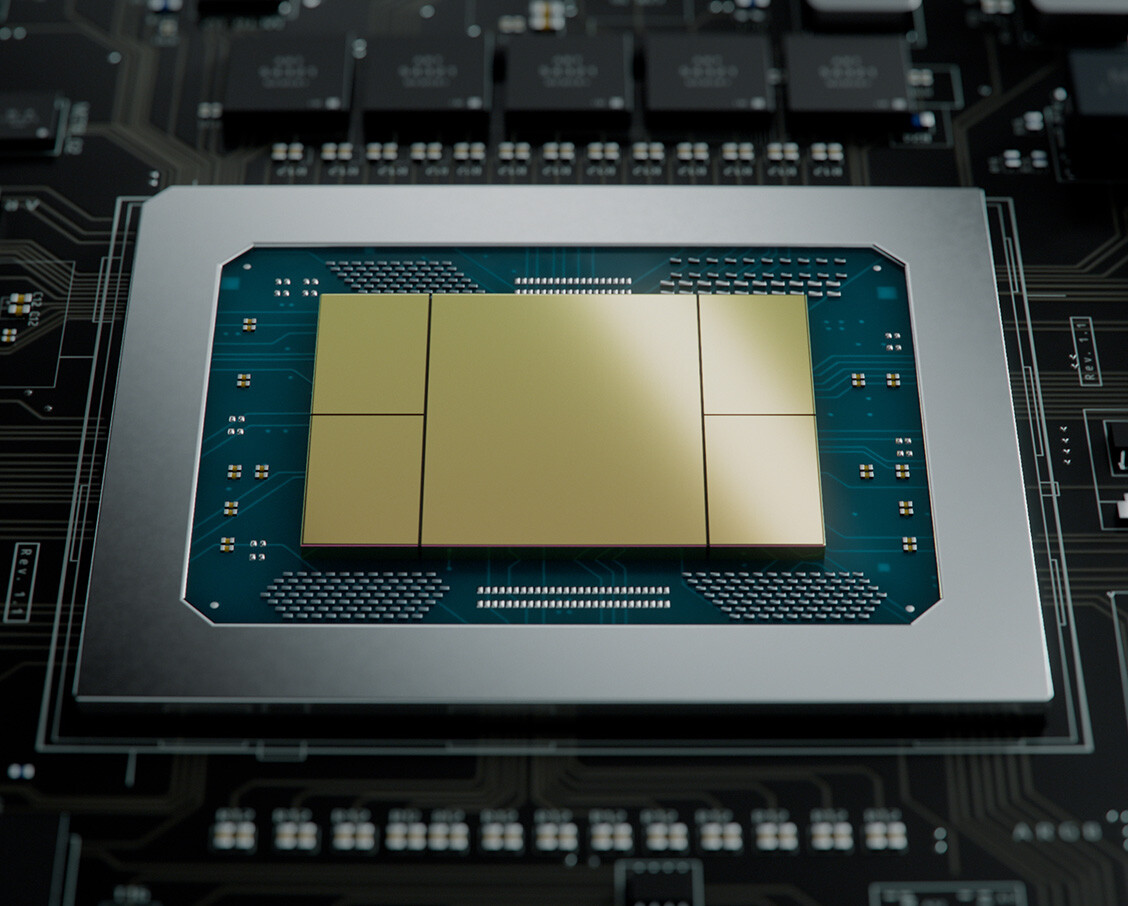

Marvell 推出2nm 64Gbps 双向芯粒接口,带宽密度超 UCIe 三倍

快速阅读: 美满电子推出2纳米64Gbps双向芯粒互连接口IP,带宽密度超30Tbps/mm,面积需求降至传统方案15%,功耗降低75%,支持冗余通道与自动修复,助力XPU性能提升与功耗降低。

美满电子(Marvell)宣布推出业界首个2纳米制程64Gbps双向芯粒互连(D2D)接口IP,旨在帮助芯片设计人员在提升新一代XPU带宽和性能的同时降低功耗和芯片面积。

Marvell介绍,该技术通过单线实现32Gbps的双向同时通信,并提供2纳米与3纳米工艺版本。其主要技术特性包括:

– **带宽密度**:超过30Tbps/mm,是UCIe标准同速方案的3倍以上。

– **面积优化**:在最小深度配置下,计算芯粒面积需求可降低至传统方案的15%。

– **功耗优化**:采用自适应功耗管理技术,可根据数据中心突发流量自动调节设备活动,常规负载下接口功耗可降低75%,高峰流量期间可降低42%。

– **可靠性增强**:支持冗余通道与自动修复,减少比特错误率,提高良率。

除D2D物理层技术外,Marvell还提供包括应用桥、链路层与物理互连在内的完整解决方案栈,以缩短客户新一代XPU的上市周期。

Marvell最早于2024年3月宣布推出2纳米平台;2025年3月展示了可运行的2纳米芯片成果,随后又发布了2纳米定制SRAM技术。此次推出的2纳米与3纳米节点下的64Gbps D2D接口,延续了这一技术发展路径。

根据Marvell的定制化战略,公司通过系统与半导体设计、先进工艺制造以及涵盖SerDes、2D/3D芯粒互连、硅光子、定制HBM、SoC互连结构、光学I/O与PCIe Gen7接口在内的完整半导体平台解决方案,推动技术创新。

(以上内容均由Ai生成)