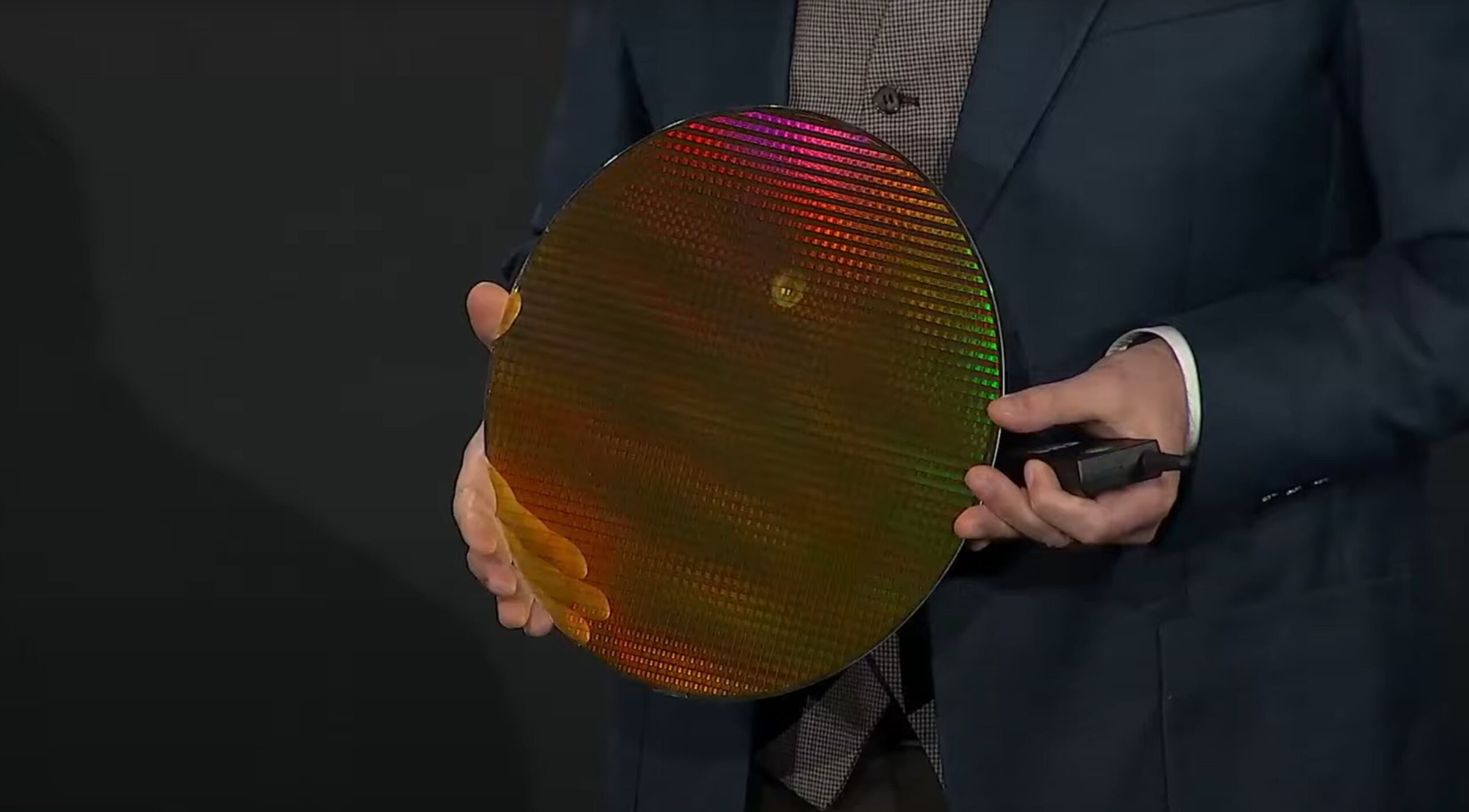

铠侠和闪迪开始出货 BiCS9 3D NAND 样品——将 112 层 BiCS5 与现代 CBA 和 DDR6.0 接口相结合的混合设计,可实现更高的性能和成本效益

快速阅读: 据《汤姆的硬件》称,铠侠推出采用CBA技术的BiCS9闪存芯片,将逻辑与存储晶圆键合,支持最高3.6 Gb/s的Toggle DDR 6.0速率,峰值达4.8 Gb/s。

据媒体报道,近日,铠侠宣布推出采用CMOS直接键合到阵列(CBA)技术的BiCS9闪存芯片。这种混合结构通过将逻辑单元晶圆和存储单元晶圆在优化条件下分别制造,再键合在一起,形成高性能封装。这一创新使得铠侠能够将成熟的单元结构,如112层的BiCS5或218层的BiCS8,与现代I/O接口结合。新推出的芯片最高支持3.6 Gb/s的Toggle DDR 6.0速率,在特定测试条件下,峰值速率可达4.8 Gb/s。

(以上内容均由Ai生成)