AMD 预告其首款 2nm 芯片 EPYC“Venice”在台积电 N2 节点上制造——还宣布在美国生产最新一代芯片

快速阅读: 据《Tom 的硬件》称,AMD宣布获得首批台积电2纳米级N2工艺芯片,用于第六代EPYC“威尼斯”处理器CCD,预计2026年发布。这展示了AMD与台积电紧密合作的成果及技术领先地位。

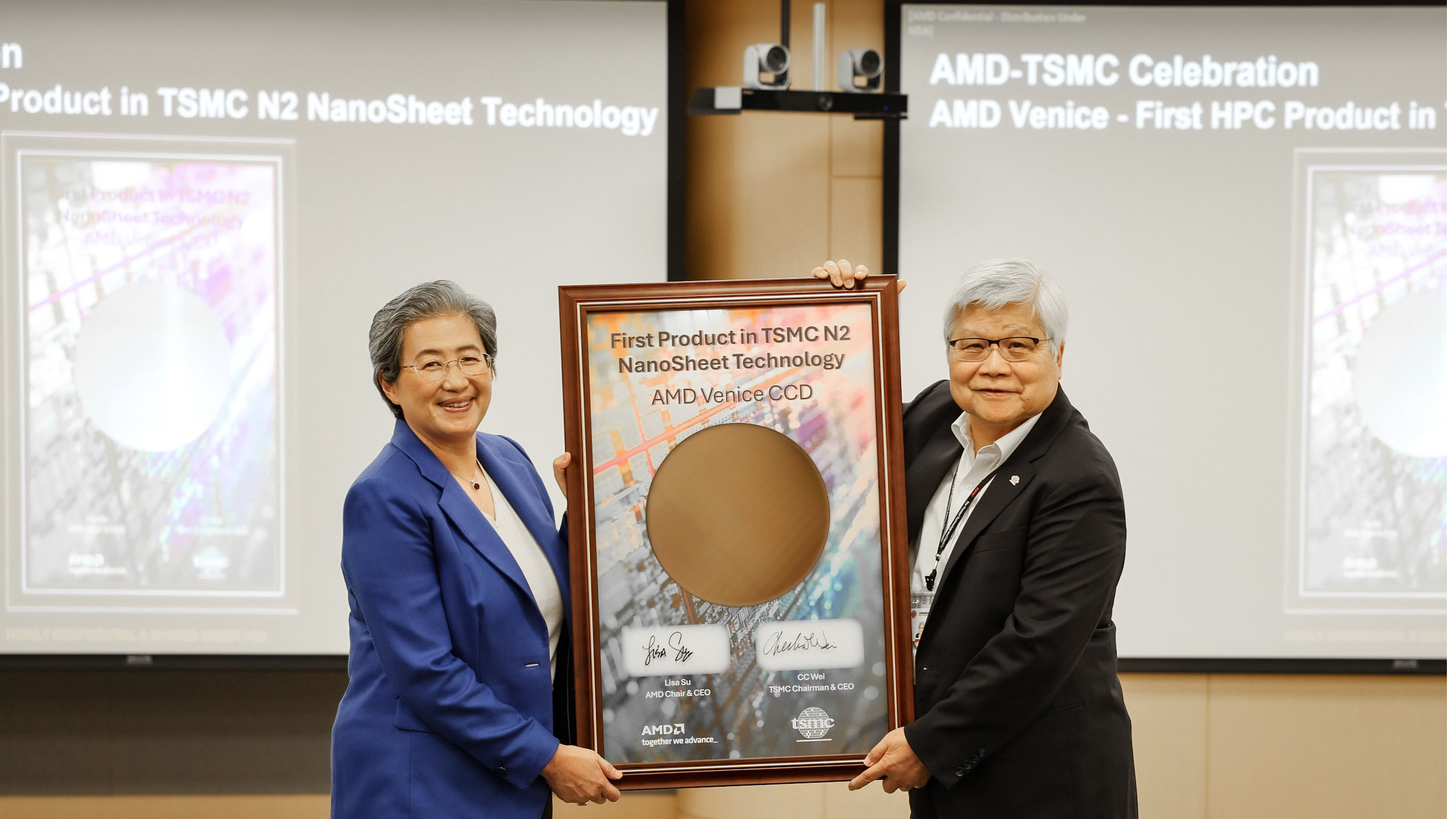

AMD周一晚间意外宣布,已获得了首批采用台积电N2工艺的2纳米级芯片,这将是其第六代EPYC“威尼斯”处理器的核心复合芯片(CCD),预计将于明年发布。威尼斯CCD是业内首款基于台积电N2工艺的高性能计算(HPC)CPU设计,彰显了AMD积极进取的产品路线图以及台积电生产工艺的成熟度。

AMD的第六代EPYC“威尼斯”预计将基于公司的Zen 6微架构,并计划于2026年推出。该CPU将使用台积电N2(2纳米级)工艺制造的CCD,因此现在是AMD从工厂获得首批威尼斯CCD的时候了。然而,AMD已经拥有可以讨论的芯片这一事实,突显了AMD与台积电之间长期的合作关系,以及双方共同努力在台积电迄今为止开发的最先进工艺技术之一上构建芯片的成果。

目前,AMD并未详细讨论其EPYC“威尼斯”处理器或CCD的具体信息,但公司新闻稿称硅片已完成验证并成功启动,这意味着CCD已成功通电并通过了基本功能测试和验证。

或许你也会感兴趣:

– 比较英特尔18A和台积电N2工艺节点:英特尔速度更快,但台积电密度更高

– 基于AMD Zen 6架构的桌面处理器可能最多配备24个核心

“多年来,台积电一直是我们的关键合作伙伴,我们与其研发和制造团队的深入合作使AMD能够持续推出推动高性能计算极限的领先产品,”AMD首席执行官苏姿丰博士表示。“成为台积电N2工艺和亚利桑那Fab 21工厂的领先高性能计算客户,是我们紧密合作推动技术创新并提供未来计算所需先进技术的绝佳例证。”

台积电的N2是该代工厂首次采用环绕栅极(GAA)纳米片晶体管的工艺技术。该公司预计其制造技术将在恒定电压下实现24%至35%的功耗降低或15%的性能提升,同时相比之前的N3(3纳米级)一代晶体管密度提高1.15倍。这些改进主要得益于新型晶体管类型和N2 NanoFlex设计技术协同优化框架。

AMD的公告是在其宿敌英特尔推迟其下一代基于18A制造技术(旨在与台积电N2竞争)的Xeon“清水森林”处理器发布时间到明年的上半年之后发布的。

此外,AMD宣布其第五代EPYC处理器由台积电在亚利桑那州菲尼克斯附近的Fab 21工厂生产的硅片已成功通过验证。结果,公司的一些当前一代EPYC CPU现在可以在美国生产。

紧跟前沿:订阅Tom’s Hardware通讯

直接获取Tom’s Hardware的最新资讯和深度分析。

紧跟前沿:订阅Tom’s Hardware通讯

我们代表我们的可信合作伙伴或赞助商向您发送电子邮件。

“我们很自豪AMD能成为我们先进的2纳米(N2)工艺技术和台积电亚利桑那工厂的领先高性能计算客户,”台积电首席执行官兼董事长魏哲家博士说。“通过合作,我们正在推动显著的技术进步,从而为高性能硅带来更好的性能、功率效率和产量。我们期待继续与AMD密切合作,引领计算新时代的到来。”

查看更多CPU新闻

查看所有评论(0)

安东·希洛夫

社交媒体链接

特约作者

安东·希洛夫是Tom’s Hardware的特约作者。在过去几十年里,他报道了从CPU和GPU到超级计算机的一切,以及现代制造技术和最新工厂工具到高科技行业趋势等。

(以上内容均由Ai生成)