富士通2031年实现CPU+NPU融合芯片

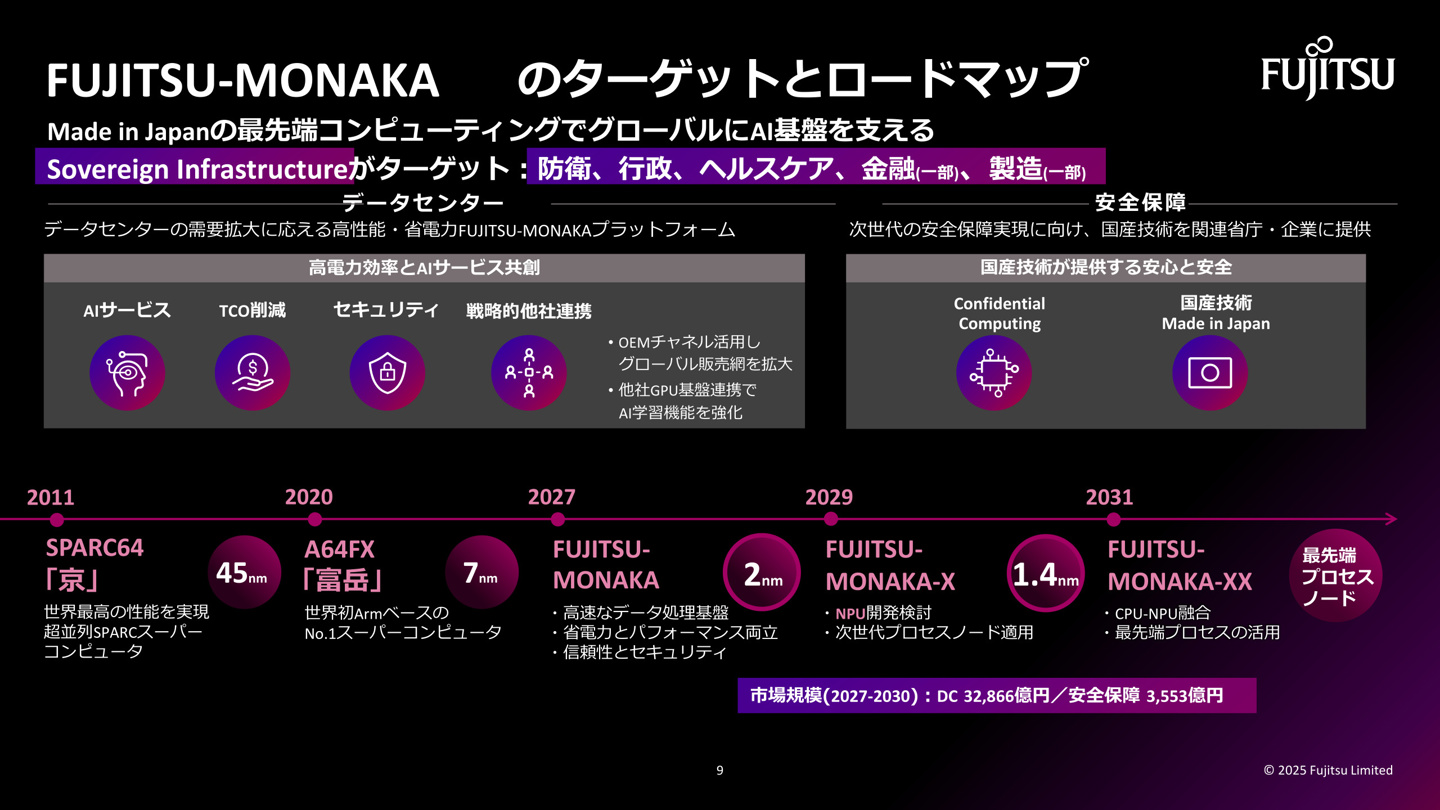

快速阅读: 富士通公布HPC与量子芯片开发路线图,计划2027年起每两年迭代HPC处理器,2029年MONAKA-X采用1.4纳米工艺,2031年MONAKA-XX融合CPU与NPU架构;量子计算目标2030年实现1000量子比特。

富士通在 2025 年 10 月 30 日日本经济产业省产业结构审议会绿色创新项目部会产业结构转型领域工作组的第 34 次会议上,公布了其传统高性能计算机(HPC)与量子芯片的开发路线图。在 HPC 处理器方面,富士通计划从 2027 年的 FUJITSU-MONAKA 开始,每两年进行一次迭代更新。继初代 MONAKA 之后,2029 年推出的 MONAKA-X 将采用 1.4 纳米制程工艺,并研究引入神经网络处理器(NPU)。2031 年的 MONAKA-XX 则旨在实现 CPU 和 NPU 架构的融合,并应用最先进的工艺技术。

在量子计算领域,富士通的目标是在 2030 年实现 1000 量子比特/250 逻辑量子比特的集成,并在此基础上进一步扩展至 1000 逻辑量子比特。

(以上内容均由Ai生成)